Fundraising

Supporting deep-tech start-ups in their process of raising venture capital. We maintain a global network of (deep-tech focused) (C)VCs with direct access on partner-level.

The TD Shepherd team has been helping technology companies successfully navigate the maze of corporate finance since 2014. We have successfully completed over 100+ transactions, ranging from fundraising to exit to fund-for-fund and other strategic services within the deep-tech eco-system. Our customers range from early-stage startups, incubators, VCs and CVCs all the way to smaller and larger corporates in the North American and European geography. All these customers share a common feature: being active in the deep-tech eco-system.

TD Shepherd is a deep-tech corporate finance firm that facilitates optimized transactions for its clients. We do this through a unique combination of engineering and commercial expertise and experience. Our Associates are global (including the Silicon Valley, Canada, The Netherlands, Germany and the UK) so we can expand the international reach of our clients to maximize their opportunities.

Our primary focus areas encompass deep technologies, with a particular emphasis on:

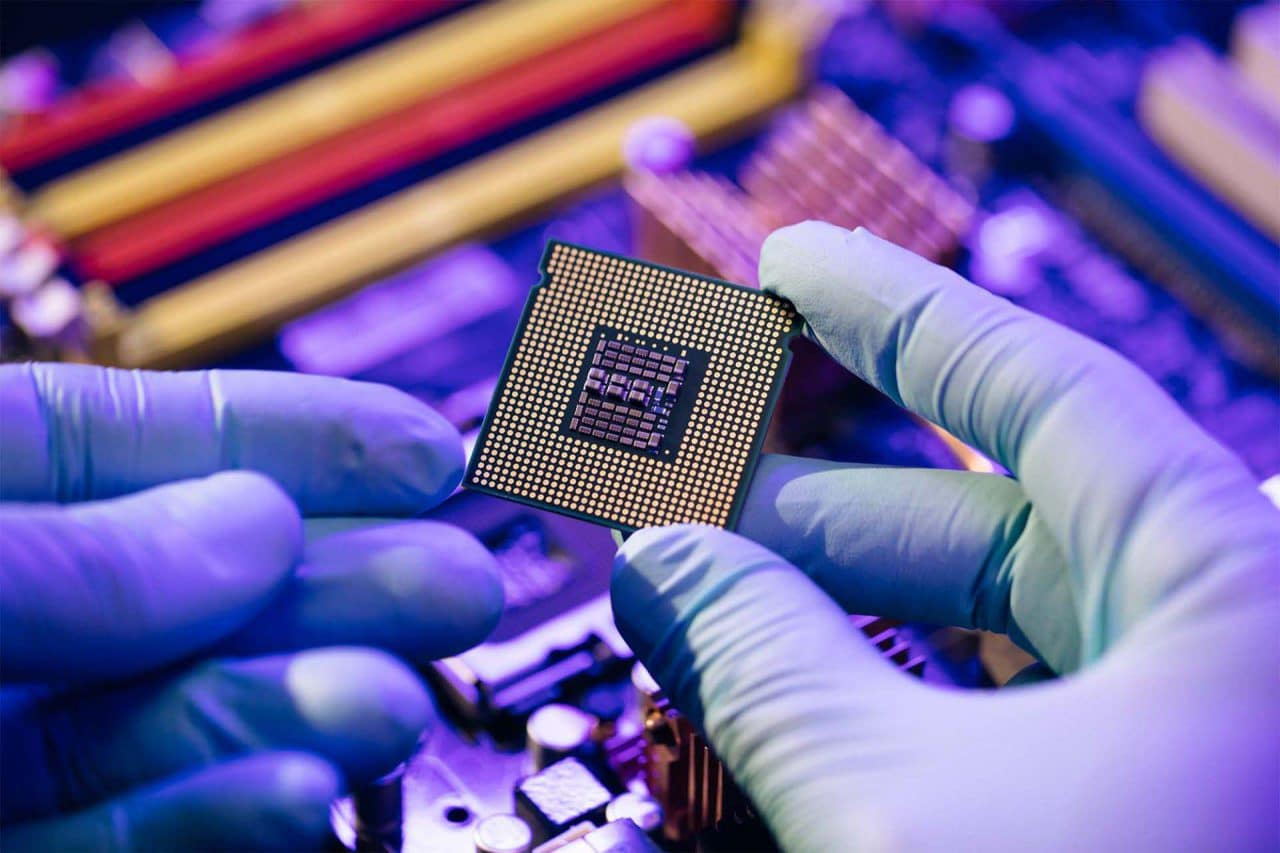

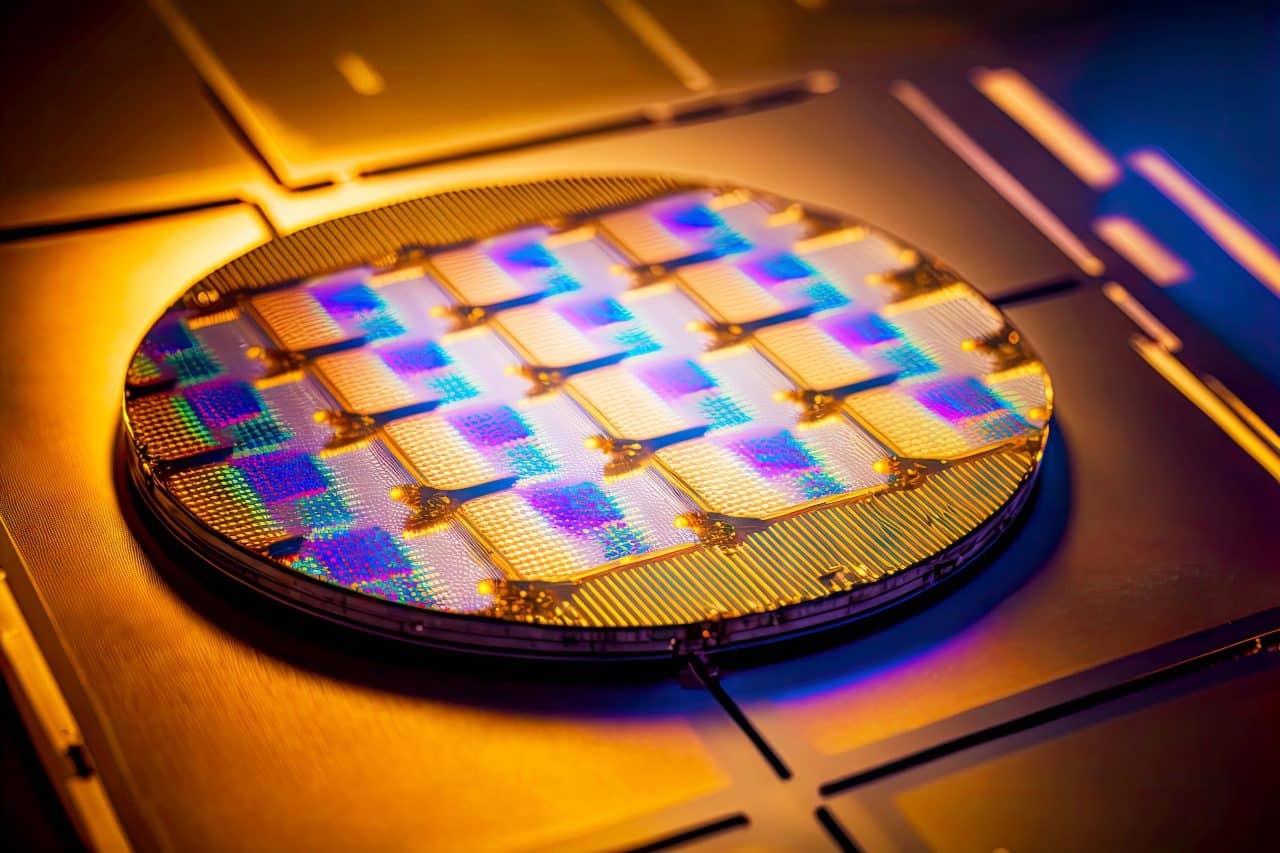

A significant part of TD Shepherd’s team has a background in the semiconductor industry, ranging from equipment and materials, fabrication, process line management to design, characterization, and test of semiconductor devices. This includes such disciplines as MEMS, (embedded) DRAM, standard cell, SRAM and I/O library design and high-speed arithmetic. Positions held by Associates cover both the technical and the marketing/sales side of the semiconductor business. Experience covers several semiconductor startups with successful exits as well as large corporates/IDMs.

TD Shepherd has extensive experience in photonics. We were part of the initial founding steps and subsequent roadmap of companies like EFFECT Photonics, a company focused on PiCs based on InP technology. We’ve advised photonics companies on manufacturing-, product- and market strategy and helped establish strategic partnerships with key players in the industry.

Neither regular semiconductors or any of its “off-shoots”, photonics or related technologies can function without the use of Electronic Design Tools (EDA). Having been part of the EDA since the early days, we understand the role it plays in the different fields and the continued innovation required to keep pace with the technologies it is serving. The continued increasing complexity, the drive for chiplets-based solutions, and the use of alternative power strategies provides enough room for startups to develop innovative solutions. Further developments on the geopolitical front create both new complexities as well as new opportunities.

The developments on the hardware level are driving continued innovation on the embedded software level. However, the developments here are much slower and mostly determined by the regular software development. Embedded software comes with very specific requirements ranging from multi-core to heterogeneous load scheduling. Startups like Vector Fabrics and Silexica were both pioneering in this field, with TD Shepherd as part of their path. Today’s innovation continues along such paths as well as developing new concepts along the AI/ML path where software is quickly becoming a distinguishing factor in the ability to demonstrate superior hardware solutions.

Like any responsible community member, TD Shepherd has evaluated its modus operandi to ensure it can make a proper contribution to becoming carbon neutral. Starting in 2022, the company has changed its travel guidelines. Priority is on trains for travel throughout Europe.

Over 2024-2026, TD Shepherd will implement a carbon compensation model to offset its travel through an appropriate compensation scheme.

TD Shepherd has and continues to contribute to the deep-tech industry through its membership of IEEE and several of its societies. We are equally pursuing the diversification of our team as a key priority. This requires a longer-term strategy focusing on growing the team in specific geographies and bringing on board new expertise.

These numbers tell our story. Uniquely for a corporate finance firm, 80% of our team have worked as engineers, so we really understand deep-tech innovation. 40% of the team have been founders of deep-tech start-ups and 30% have worked as partners or associates in a VC. This means we have a 360-degree view of business propositions and transactions, so we’re perfectly placed to support you in your next steps.

“Over 100 transactions successfully completed in the last 10 years.”

Our services will save you valuable time, effort, and expense. To streamline every transaction, we bring an established network of relevant VC, PE, and corporate partners, complemented by relationships with government bodies involved with deep-tech funding, and with independent financial and legal specialists.

“Partnering with TD Shepherd means reducing your transaction risk while accelerating the process, and an optimized outcome for all parties.”

In a nutshell: TEAM, EXPERTISE, EXPERIENCE and NETWORK. Whatever your objective, whatever your “Next Step” entails, our deep-tech expertise and network ensures a tailored approach and effective execution. Each company has its own fingerprint and, with that unique fingerprint, comes a unique strategy and execution. Not only brings our team a history of more than 100 successfully executed deep-tech projects—from M&A to fundraising to due diligence—it also brings a network across the deep-tech eco-system that is unmatched by any other corporate finance company operating in this space.

We speak your language; as a sparring partner we provide expert input and guidance on how to optimally represent the value pillars of the company, how to position it in its competitive field and how to align its roadmap with its ambition and strategy.

The TD Shepherd team will quickly understand your deep-tech proposition, help you position it clearly to attract investors, help you find the right investment partner(s), and ensure you strike the optimum deal. A partnership with TD Shepherd means you gain more time during the process to focus on your business priorities and grow your company. And as you take your next steps, our deep-tech consulting services are available to support you as your business grows.

Where we’re acting on behalf of buyers, we have the deep-tech knowledge and experience to, where and when necessary, sharpen your acquisition strategy. We are able to identify and expertly evaluate the businesses that provide the best fit for achieving your objectives while you remain at arm’s length until the best opportunity has been identified.

The TD Shepherd team will use its deep-tech experience and global contacts to find buyers with the best fit to help you achieve your goals, both at exit and post-exit. The team will work with you to position your business and to clearly communicate your value proposition. We’ll help simplify and streamline the sales process and protect your interests, giving you more time to grow your business and make it more attractive to acquirers.

Part of what makes us such trusted advisors is our reputation for understanding the customer’s business, not just the financials. As former executives, fund managers and entrepreneurs, we bring both broad and deep experience from which we build a project team that fits the challenge. We are fortunate to have a strong team of very senior Associate Directors, who are specialists in their areas of expertise.

Starting a deep tech startup is challenging, with various hurdles to overcome. Networking is crucial for success in this space. It enables entrepreneurs to connect with like-minded individuals, investors, and potential customers.

Building a strong team for a deep tech startup involves a combination of strategic planning, effective recruitment, and creating a positive work environment.

To ensure that your startup project will grow smoothly, it is a must to attract talent and build a strong team.

Deep tech startups are at the forefront of technological advancements, creating cutting-edge solutions that shape the future. However, without effective marketing strategies, these startups may struggle to gain visibility, secure funding, and attract customers.